З¶ИлКҪУІјюЧЁјТИрИшөзЧУРыІјНЖіцКЧҝо»щУЪГв·СҝӘ·ЕөД RISC-V ЦёБојҜјЬ№№ (ISA) өДНкИ«ЧФЦчСР·ўөДҙҰАнЖчДЪәЛЎЈ

ЦЪЛщЦЬЦӘЈ¬ФЪ№эИҘЈ¬ёГ№«ЛҫТСҫӯНЖіцБЛІЙУГҫ§РДҝЖјјRISC-VДЪәЛөДІъЖ·Ј¬Из32О»УпТфҝШЦЖASSPЎўөз»ъҝШЦЖASSPәН64О»НЁУГОўҙҰАнЖч“RZ/Five”Ј¬ө«Ль»№Г»УРАыУГНЁ№эХвПојјКхЈ¬ёГ№«ЛҫјЖ»®МбёЯЖдФЪ RISC-V КРіЎөДөШО»ЎЈ

ИрИшөзЧУөД Giancarlo Parodi ФЪМёөҪёГјјКхКұұнКҫЈә“RISC-V ISA ФЪ°лөјМеРРТөЦРөДИХТжЖХј°КЗҙҙРВөДёЈТфЎЈЛьОӘЙијЖИЛФұМṩБЛЗ°ЛщОҙУРөДБй»оРФЈ¬ІўҪ«»әВэ¶шОИ¶ЁөШМфХҪәНёДұдЗ¶ИлКҪПөНіөДөұЗ°ёсҫЦЎЈ”ёГ№«ЛҫЧоРВөДОўҝШЦЖЖчөДұіәуЎЈ“№эИҘЈ¬ИрИшөзЧУТСҫӯІЙУГБЛ RISC-V јјКхЈ¬ТэИлБЛ»щУЪ Andes Technology Corp ҝӘ·ўөД CPU ДЪәЛ№№ҪЁөДУГУЪУпТфҝШЦЖәНөз»ъҝШЦЖөД 32 О» ASSP ЖчјюЎЈБоИЛРЛ·ЬөДПВТ»ІҪКЗ[ОТГЗөД]КЧҝоДЪЦГ -ДЪІҝЙијЖөД CPU әЛРДЎЈ

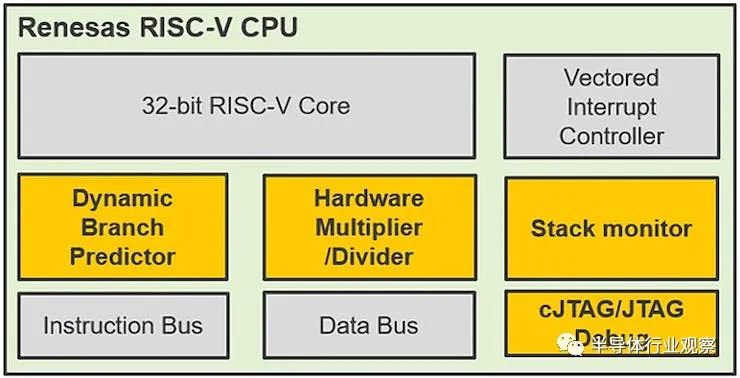

ЛдИ»ИрИшөзЧУЙРОҙНёВ¶Ҫ«К№УГЖдДЪІҝәЛРДөДІҝјюөДНкХыІъЖ·ПёҪЪЈ¬ө«ЛьТСҫӯИ·ИПБЛУР№ШәЛРДұҫЙнөДТ»Р©јјКхПёҪЪЎЈҝтНјПФКҫБЛөҘёц 32 О» RISC-V ДЪәЛЈ¬ҫЯУРРФДЬМбЙэөД¶ҜМ¬·ЦЦ§ФӨІвЖчЎўУІјюіЛ·ЁЖч/іэ·ЁЖчЎўПтБҝЦР¶ПҝШЦЖЖчЎў¶СХ»јаКУЖчјДҙжЖчЎў¶АБўөДЦёБоәНКэҫЭЧЬПЯТФј°ҪфҙХРН JTAG (cJTAG)/ JTAG өчКФ№ҰДЬЎЈЛь»№іРЕө 3.27 CoreMark/MHz)өДРФДЬЛ®ЖҪ——ҫЎ№ЬКұЦУЛЩ¶ИЙРІ»ЗеіюЎЈ

“ёГ CPU ККУГУЪРн¶аІ»Н¬өДУҰУГ»·ҫіЎЈЛьҝЙТФУГЧчЦч CPU »т№ЬАнЖ¬ЙПЧУПөНіЈ¬ЙхЦБЗ¶ИлөҪЧЁГЕөД ASSP [МШ¶ЁУҰУГұкЧјІъЖ·] ЙиұёЦРЈ¬”Parodi ЙщіЖЎЈ“ПФИ»Ль·ЗіЈБй»оЎЈЖдҙОЈ¬ФЪ№иЖ¬Гж»э·ҪГжЈ¬ёГКөК©·ЗіЈёЯР§Ј¬іэБЛ¶ФіЙұҫУ°ПмҪПРЎөДГчПФР§№ыЦ®НвЈ¬»№УРЦъУЪҪөөНҙэ»ъЖЪјдөД№ӨЧчөзБчәНВ©өзБчЎЈөЪИэЈ¬ҫЎ№ЬХл¶ФРЎРНЗ¶ИлКҪПөНіЈ¬ө«ЛьМṩБЛБоИЛҫӘСИөДёЯЛ®ЖҪјЖЛгНМНВБҝЈ¬ЙхЦБҝЙТФВъЧгЙо¶ИЗ¶ИлКҪУҰУГИХТжҝБҝМөДРФДЬТӘЗуЎЈ”

ёГәЛРДАыУГГв·СҝӘ·ЕөД RISC-V ЦёБојҜјЬ№№ј°Жд¶аёцА©Х№ЈәParodi ұнКҫЈ¬ёГәЛРДКөПЦБЛҙшУРіЛ·Ё (M)ЎўФӯЧУ·ГОК (A)ЎўС№ЛхЦёБо (C) өД RV32I »т RV32E ISA Ј¬ТФј°О»ІЩЧч (B) А©Х№ЎЈParodi ЙщіЖЈә“ХвҫНКЗ RISC-V ISA ёЕДоөДГАГоЦ®ҙҰЈ¬ЛьКЗҙУН·ҝӘКј№№ҪЁөДЈ¬ФКРнЙијЖИЛФұёщҫЭДҝұкУГАэСЎФсТӘ°ьә¬ФЪҙҰАнЖчЦРөДФӘЛШЈ¬ІўЧоЦХУЕ»ҜУЙҙЛІъЙъөД№ҰәДЎўРФДЬәНРҫЖ¬ХјУГҝХјдЦ®јдөДИЁәвЎЈ”

ИрИшөзЧУұнКҫЈ¬ДҝЗ°ХэФЪПт“ҫ«СЎҝН»§”МṩҙшУРРВДЪәЛөДРҫЖ¬СщЖ·Ј¬КЧЕъЙМУГРҫЖ¬Ҫ«УЪГчДкөЪТ»јҫ¶ИНЖіцЎЈ

RISC-V өДәЛРДЈәРВКУТ°

RISC-V ISA ФЪ°лөјМеРРТөЦРөДИХТжЖХј°КЗҙҙРВөДёЈТфЎЈЛьОӘЙијЖИЛФұМṩБЛЗ°ЛщОҙУРөДБй»оРФЈ¬ІўҪ«»әВэ¶шОИ¶ЁөШМфХҪәНёДұдЗ¶ИлКҪПөНіөДөұЗ°ёсҫЦЎЈ№эИҘЈ¬ИрИшөзЧУФшІЙУГ RISC-V јјКхЈ¬НЖіц»щУЪҫ§РДҝЖјјҝӘ·ўөД CPU ДЪәЛөД 32 О» ASSP ЙиұёЈ¬УГУЪУпТфҝШЦЖәНөз»ъҝШЦЖЎЈ

БоИЛРЛ·ЬөДПВТ»ІҪКЗөЪТ»ёцДЪІҝЙијЖөД CPU ДЪәЛөДНЖіцЎЈCPU өДёЯј¶ҝтНјИзПВЛщКҫЈә

ө«ЛьУРКІГҙМШұрЦ®ҙҰДШЈҝКЧПИЈ¬ёГCPUККУГУЪРн¶аІ»Н¬өДУҰУГ»·ҫіЎЈЛьҝЙТФУГЧчЦч CPU »т№ЬАнЖ¬ЙПЧУПөНіЈ¬ЙхЦБЗ¶ИлөҪЧЁУГ ASSP ЙиұёЦРЎЈПФИ»Ль·ЗіЈБй»оЎЈЖдҙОЈ¬ёГКөК©·Ҫ°ёФЪ№иГж»э·ҪГж·ЗіЈёЯР§Ј¬іэБЛіЙұҫУ°ПмҪПРЎөДГчПФР§№ыНвЈ¬»№УРЦъУЪҪөөНҙэ»ъЖЪјдөД№ӨЧчөзБчәНВ©өзБчЎЈөЪИэЈ¬ҫЎ№ЬЛьХл¶ФөДКЗРЎРНЗ¶ИлКҪПөНіЈ¬ө«ЛьМṩБЛБоИЛҫӘСИөДёЯЛ®ЖҪјЖЛгНМНВБҝЈ¬ЙхЦБҝЙТФВъЧгЙо¶ИЗ¶ИлКҪУҰУГИХТжҝБҝМөДРФДЬТӘЗуЎЈ

ФЪҙЛ»щҙЎЙПЈ¬КөК©ХЯҝЙТФФЪ RV32“I”»т“E”СЎПоЦ®јдҪшРРСЎФсЈ¬ТФУЕ»ҜНЁУГјДҙжЖчөДҝЙУГКэБҝЎЈАэИзЈ¬ФЪРЎРНЧУПөНіІ»РиТӘҙҰАнёҙФУөД¶СХ»әНУҰУГіМРтө«ЧЁУГУЪ·юОсМШ¶ЁНвО§Йиұё»тЦҙРРДЪОсИООсөДЗйҝцПВЎЈ

RISC-V ISA »№ФӨјыБЛјёЦЦ“А©Х№”Ј¬ЛьГЗТФұИК№УГұкЧјЗҝЦЖ ISA ёьәГ»тёьУРР§өД·ҪКҪКөПЦМШ¶Ё№ҰДЬЎЈИрИшөзЧУСЎФсХыәПЖдЦРөДјёёцЈә

MА©Х№– јУЛЩІўУЕ»ҜіЛ·ЁЈЁәНіэ·ЁЈ©ФЛЛгЈ¬АыУГУІјюіЛ·ЁЖчәНіэ·ЁЖчөҘФӘКөПЦЧоҝмөДЦёБоЦҙРР;

AА©Х№– Ц§іЦФӯЧУ·ГОКЦёБоЈ¬ҝЙЧчОӘІў·ўәН¶АХј·ГОК№ЬАнөД»щҙЎЈЁНЁіЈФЪ»щУЪ RTOS өДПөНіЦРЈ©;

C А©Х№– ¶ЁТеҪцТФ 16 О»ұаВлөДС№ЛхЦёБоЈ¬МШұрУРИӨЈ¬ТтОӘЛьГЗҝЙТФЗбЛЙөШОӘіЈјыәНЖө·ұЦёБоҪЪКЎДЪҙжҝХјдЈ¬ҙУ¶шФКРнұаТлЖчФЪҝЙДЬөДЗйҝцПВСЎФсХвР©УЕ»ҜЈ»Т»ёцјтөҘөДјјЗЙЈ¬ҝЙТФЛхРЎҙъВлІўН¬КұМбёЯРФДЬ;

B А©Х№– МнјУБЛ¶аёцО»ІЩЧчЦёБоЈ¬Хв¶ФУЪ»щУЪО»УтұаВлЦө№ЬАнНвЙијДҙжЖчЎўРӯТйәНКэҫЭҪб№№өДУҰУГіМРтАҙЛөҫЯУРО»УЕКЖЈ¬ЖдЦРТ»ЧйЧйіЙөДНЁУГЦёБоөД№ҰДЬНЁіЈҝЙТФУЙөҘёцЧЁУГЦёБоҙъМж;

ХвҫНКЗ RISC-V ISA ёЕДоөДГАГоЦ®ҙҰЈ¬ЛьКЗҙУН·ҝӘКј№№ҪЁөДЈ¬ФКРнЙијЖИЛФұёщҫЭЖдДҝұкУГАэСЎФсТӘ°ьә¬ФЪҙҰАнЖчЦРөДФӘЛШЈ¬ҙУ¶шУЕ»ҜУЙҙЛІъЙъөД№ҰәДЎўРФДЬәНРҫЖ¬ХјУГҝХјдЎЈҙУ№ӨіМҪЗ¶ИАҙҝҙЈ¬ХвКЗТ»ЦЦ·ЗіЈУЕСЕөД·ҪКҪЈ¬ҝЙТФИ·ұЈДъЦ»ОӘДЗР©ДъХжХэПлТӘКөПЦөДКВЗй“ё¶іцҙъјЫ”ЎЈ

ОӘБЛФцЗҝУҰУГИнјюөДВі°фРФЈ¬МнјУБЛ¶СХ»јаҝШјДҙжЖчЎЈХв¶ФУЪјмІвәН·АЦ№¶СХ»ДЪҙжТзіц·ЗіЈУРУГЈ¬ХвКЗ·ЗіЈіЈјыөДОКМвЈ¬ө«УРКұәЬДСҪцНЁ№эІвКФёІёЗВКАҙ·ўПЦЎЈУЙУЪХвР©ОКМвҝЙДЬ»бЛрәҰПөНіөДНкХыРФІўФЪФЛРРКұІъЙъУҰУГіМРтҙнОуРРОӘЈ¬ТтҙЛХвКЗТ»ёц·ЗіЈәГөД№ҰДЬЈ¬ТІКЗҝШЦЖҙЛАаІ»ҝЙФӨјыКВјюөД»щұҫ°ІИ«НшЎЈ

јҙК№КЗЧојтөҘөДҝШЦЖПөНіНЁіЈТІұШРл№ЬАн¶аёцҫцІЯВ·ҫ¶АҙОӘУҰУГіМРтМṩ·юОсІўЛжКұөчУГККөұөДҙҰАнАэіМЎЈ»тХЯ¶ФКэҫЭ»әіеЗш·ҙёҙЦҙРРТ»Р©ЦШёҙјЖЛгЎЈТтҙЛЈ¬КөПЦөДҙъВлҪ«ҫЯУР¶аёц·ЦЦ§ЎўСӯ»·әНҫцІЯөгЈ¬ЖдЦРіМРтБчіМҝЙДЬ»бёщҫЭЙППВОД¶шёДұдЎЈУЙУЪХвЦЦДЈКҪәЬіЈјыЈ¬CPU »№ҫЯУР¶ҜМ¬·ЦЦ§ФӨІвөҘФӘЈ¬ТФК№ҙЛАаҙҰАнёьјУёЯР§ЎЈ·ЦЦ§ФӨІвЖчөДЧчУГКЗ№ЫІмҙъВлРРОӘЈ¬И»әу¶ҜМ¬НЖ¶ПФЪҙЛАаҝШЦЖСӯ»·ЖЪјдЧоУРҝЙДЬЦҙРРөДПВТ»МхЦёБоЎЈИз№ыОТГЗјЩЙиЛьФЪХв·ҪГжЧцөГәЬәГЈ¬ДЗГҙФЪСЎФсПВТ»МхТӘ»сИЎЦҙРРөДЦёБоКұЧціцХэИ·өДІВІвЈ¬ЛьҪ«ПФЧЕМбёЯЖҪҫщҙъВлЦҙРРНМНВБҝЎЈ

ПВТ»ёцТӘМбөҪөД№№ҪЁҝйУлөчКФ№ҰДЬУР№ШЎЈіэБЛұкЧјJtagНвЈ¬CPU»№Ц§іЦБҪПЯҪфҙХРНJtagөчКФҪУҝЪЈ¬·ЗіЈККәПУГ»§УҰУГТэҪЕКэБҝУРПЮөДЧоРЎОўҝШЦЖЖч·вЧ°ЎЈCPU ЦР»№КөПЦБЛ¶аёцРФДЬјаКУЖчјДҙжЖчЈ¬ҙУ¶шҝЙТФЗбЛЙөШ¶ФЛщЦҙРРҙъВлөДФЛРРКұРРОӘҪшРР»щЧјІвКФЎЈ

ИОәОЗ¶ИлКҪПөНіөДБнТ»ёц№ШјьТтЛШКЗ¶ФКВјюөДПмУҰДЬБҰЈ¬ФЪОўҝШЦЖЖчј¶ұрөДЙо¶ИЗ¶ИлКҪЙиұёЦРЈ¬УІКөКұРРОӘКЗЗҝЦЖТӘЗуөДЈ¬ХвТвО¶ЧЕУҰУГіМРтУРУРПЮөДКұјдАҙПмУҰМШ¶ЁКВјюЎЈөНПмУҰСУіЩҝЙТФҙшАҙРн¶аІ»Н¬өДәГҙҰЈәФКРнУҰУГіМРтОӘёь¶аІў·ўКВјюМṩ·юОсЈ¬МṩәПАнөДКұјдФЈ¶ИТФИ·ұЈХэИ·өДИООсҙҰАнЈ¬»тХЯҝЙДЬПЮЦЖ CPU ЛЩ¶ИТФҪЪКЎёь¶аөзБҝЎЈ

ФЪјЬ№№ІгГжЈ¬ИрИшөзЧУөДКөПЦМнјУБЛјДҙжЖчЧйұЈҙж№ҰДЬЈ¬ТФёДЙЖСУіЩІўК№ҝӘ·ўИЛФұДЬ№»ПнКЬЖдУЕКЖЎЈФЪЦР¶П·юОсөДЗйҝцПВЈ¬»тХЯөұЗ¶ИлКҪ RTOS ұШРлҪ»»»өұЗ°ЦҙРРөДПЯіМТФПмУҰКВјюКұЈ¬ҝЙТФұё·ЭәН»Цёҙ CPU №ӨЧчјДҙжЖчІўјУЛЩЙППВОДЗР»»Ј¬ҫЩБҪёцјёәхЦұҪУөДАэЧУЎЈ

ОӘБЛҪшТ»ІҪ°пЦъҝӘ·ўИЛФұ¶ФУҰУГіМРтҪшРР»щЧјІвКФІўСйЦӨЖдРРОӘЈ¬»№ҝЙТФК№УГёЯР§ЗТҪфҙХөДЦёБоёъЧЩөҘФӘЈ¬ёГөҘФӘҝЙТФҪшТ»ІҪЙоИлБЛҪвПөНіөДФЛРРКұРРОӘЎЈ

ХвёЕКцБЛУР№Ш CPU №ҰДЬөДПкПёРЕПўЈ¬ЖдЦРТ»Р©№ҰДЬҝЙТФёщҫЭУҰУГәНКРіЎТӘЗуҪшРРСЎФсЎЈө«КЗЈ¬ФЪЖА№АәНЦЖФм»щУЪХвЦЦРВјјКхөДКөјКІъЖ·КұЈ¬»№УҰёГҝјВЗКІГҙЈҝКЧПИЈ¬ЛщРиөД№ӨҫЯБҙҝЙЧчОӘҝӘ·ўәНІҝКрҪвҫц·Ҫ°ёЛщРи»щҙЎЙиК©өДТ»Іҝ·ЦЎЈҝН»§Ҫ«ДЬ№»КЬТжУЪҙшУРЕдЦГІејюөД Renesas e 2 studio »·ҫі»тИОәОЦ§іЦ»щУЪ RISC-V өД MCU өДЦчТӘЙМТөөЪИэ·Ҫ IDEЎЈХвР©¶јҝЙТФК№УГБЛЎЈ

ЖдҙОЈ¬CPU КөПЦІ»ҪцҪцКЗДЈДвөДЈ¬Жд№ҰДЬТСҫӯФЪХжКөөД№иІъЖ·КөПЦЦРҪшРРБЛЙијЖәНСйЦӨЎЈК№УГ»щУЪ LLVM өДҝӘФҙұаТлЖч№ӨҫЯБҙКұЈ¬іхКј»щЧјІвКФПФКҫіцБоИЛУЎПуЙоҝМөД 3.27 CoreMark/MHz РФДЬЈ¬УЕУЪКРіЎЙПөДН¬АајЬ№№ЎЈТ»ө©өЪТ»ёцІъЖ·УЪ 2024 ДкіхНЖіцЈ¬УР№ШХвТ»УЕТміЙјЁөДёь¶аПкПёРЕПўҪ«ФЪEEMBC НшХҫЙПХТөҪЎЈХэИзРн¶аИЛЛщЦёіцөДЈ¬ЧЁУРЙМТөұаТлЖчөДРФДЬТ»ө©ҫӯ№эСйЦӨЈ¬ФӨјЖҪ«ұИіхІҪҪб№ыёьёЯЎЈ

ХвҝоРВ CPU КЗәуРшІҪЦиөД»щКҜЈ¬ОӘПЦУРИрИш MCU ІъЖ·ЧйәПҙҙҪЁБЛТ»ёц¶оНвөДІ№ідСЎПоЎЈИрИшөзЧУТСЧјұёәГОӘҝН»§МṩЧо№г·әөДҪвҫц·Ҫ°ёЈ¬ЖдЦР°ьАЁІ»¶П·ўХ№өДҙҙРВ RISC-V јЬ№№ЎЈ

№І0Мх [ІйҝҙИ«Іҝ] НшУСЖАВЫ